10G EXTREME Low Latency Ethernet FPGA IP Core Solution

Hitek Systems

The 10Gbps Extreme Low Latency Ethernet FPGA IP core solution offers a fully integrated IEEE 802.3-2015 compliant package for NIC (Network Interface Card) and Ethernet switching applications. This extremely-low-latency solution is specifically targeted for demanding financial, high-frequency trading and HPC applications.

Features

- Round Trip Latency of 24.9ns + Device Specific Transceiver Latency

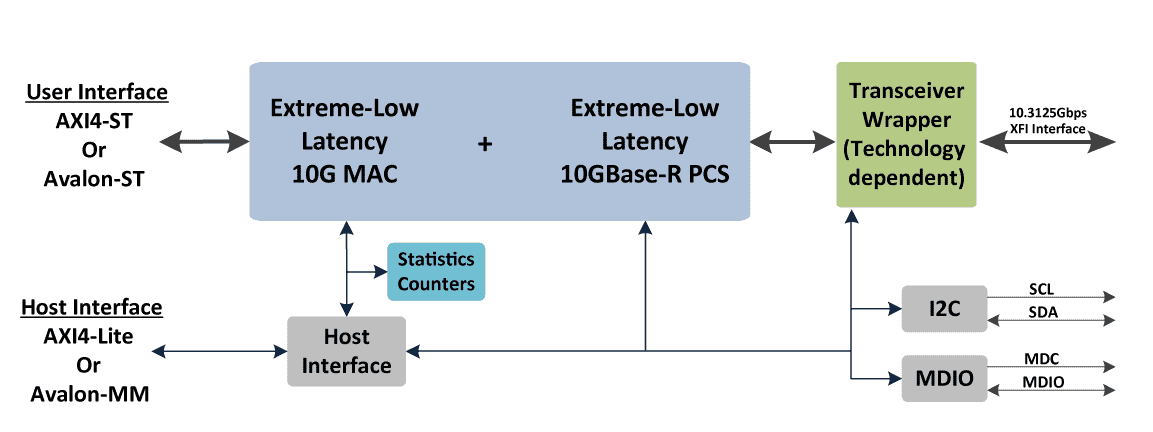

As shown in the diagram, the 10Gbps ELL Ethernet IP solution includes:

- Extreme low latency Ethernet; Tx = 7.8ns (user data in to line preamble out), Tx = 14.0ns (user data in to line data out), Rx = 10.9ns; (line data in to user data out). All latency numbers include full FCS generation and checking.

- Technology-dependent transceiver wrapper for Altera and/or Xilinx FPGAs

- Statistics counter block (for RMON and MIB)

- MDIO and I2C cores for external module and optical module status and control

Deliverables

- Encrypted MAC and PCS RTL for simulation and synthesis

- Encrypted L2 packet generator and checker RTL for simulation and synthesis

- Source code RTL (Verilog) for top-level Ethernet wrappers to allow for user specific customizations.

- Technology-specific transceiver wrappers for the selected device family

- Source code RTL (Verilog) for AXI4 Lite and Avalon-MM arbiters and address decoders

- Constraint files and synthesis scripts for design compilation

- Linux-based APIs/tools to access core configuration and statistics registers

- Design guide(s) and user manual(s)