高速訊號傳輸輔助利器-Retimer & Redriver 概論

圖一、USB & PCIE & Display Port Speed

圖一、USB & PCIE & Display Port Speed

高速訊號在通過電纜或印刷電路板傳輸時, 衰減現象很嚴重,甚至會導致訊號畸變。另外,反射、串擾、雜波訊號和散射都會導致訊號完整性與眼圖區間惡化。訊號傳輸距離增加導致訊號衰減程度加重且訊號品質下降,進而導致資料位元錯誤,無法在遠端或接收端成功復原傳輸的訊號。

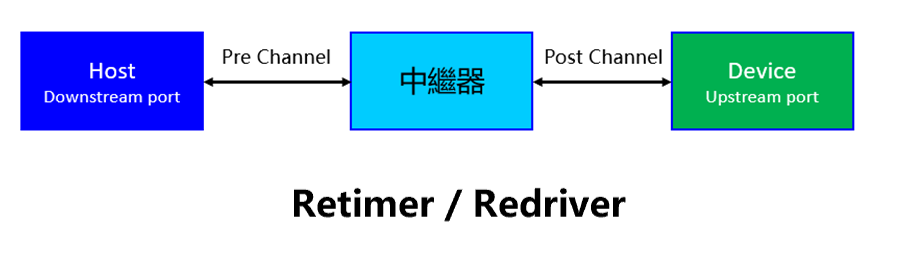

對於研發人員來說在PCB板上的佈局走線以及電纜應用無疑是另一個艱難的挑戰,對於高速訊號的傳輸應用中 ,為確保訊好品質,中繼器將是不可或缺的元件,如圖2所示,但在平時的選擇中,經常被中繼器另外的三個稱呼所混淆,不知三者的具體差異在哪兒,所以簡單的在這裡做下解釋:

基本上Repeater可以說是中繼器的統稱,以不同的架構與功能再細分為Retimer與Redriver。

圖二、Link Application

圖二、Link Application

Retimer

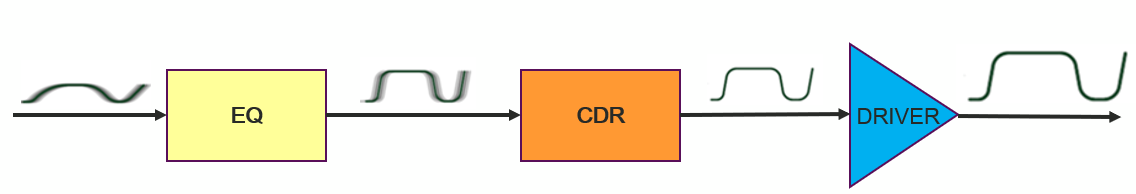

主要包含兩個功能,一個是對信號進行均衡,另一個則是對有確定性抖動和隨機性抖動的數據時鐘信號進行修復,從而輸出一個乾淨的信號給後端裝置使用。Retimer功能簡易示意圖,如圖3所示

圖三、Retimer簡易功能說明

圖三、Retimer簡易功能說明

USB IF USB 3.2 App (E)有分別說明支援USB3.2 Gen2傳輸時鐘訊號來自本地參考時鐘,與接收端復原的時鐘訊號無關的獨立參考時脈SSC(SRIS)(Separate Reference clock Independent of SSC),以及支援USB3.2 Gen1傳輸時鐘訊號來自本地參考時鐘,與接收端復原的時鐘訊號無關的數據位元BLR(Bit-Level Retimer)

SRIS

如圖3所示,這是為USB Gen2(SRIS)操作定義的架構,並且具有實體層協定感知以及軟體透明擴展設備,創建兩個獨立的電子鏈路段。如圖4所示,此架構實現了一個使用一個本地時脈作為Tx的輸入時脈,且完全獨立於Rx時脈,包括SSC的獨立參考時脈架構。

圖三、 USB3.2 Gen2操作定義的電子鏈路段

圖三、 USB3.2 Gen2操作定義的電子鏈路段

圖四、以本地時鐘作為發射機之輸入時鐘

圖四、以本地時鐘作為發射機之輸入時鐘

BLR

圖五、多抖動眼圖

圖五、多抖動眼圖

圖六、低抖動眼圖

圖六、低抖動眼圖

BLR架構具有一個實體層協定感知和軟體透明擴展設備,創建兩個獨立的電子鏈路段。如圖7所示,其所實現的是恢復時脈架構, 其所使用的是從輸入資料流程中恢復的時脈作為Tx的輸入時脈,與Rx時脈相同, 如圖8所示。

圖七、USB3.2 Gen1操作定義的電子鏈路段

圖七、USB3.2 Gen1操作定義的電子鏈路段

圖八、 以恢復時鐘作為發射機的輸入時鐘

圖八、 以恢復時鐘作為發射機的輸入時鐘

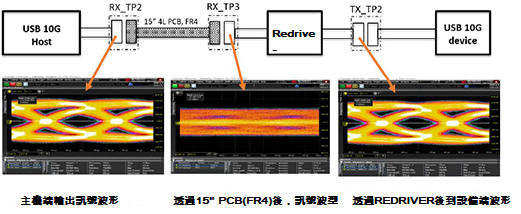

Redriver

是通過使用均衡器(EQ=Equaliztion)以及預加重控制(Pre-emphasis)技術,讓Redriver可以補償與矯正傳輸端上訊號的損失,並在接收端上恢復訊號完整性。因此可以在訊號發射端產生滿足傳送損耗的可靠訊號、以減少訊號錯誤率的眼圖 。

Redriver 功能簡易示意圖, 如圖10所示

圖十、Redriver 簡易功能說明

圖十、Redriver 簡易功能說明

- 增衡器 (Equaliztion) 技術

均衡器實際上是一個高通濾波器,如圖10所示, 是一個簡單的高通濾波器。均衡器通常是用濾波器來達成,使用濾波器來補償失真的脈衝。均衡器直接從傳輸的實際數位訊號中根據某種算法不斷調整增益,因而能適應傳輸時的信號隨機變化,使均衡器總是保持最佳的狀態,從而有更好的失真補償性能。

圖十一、高通濾波器

圖十一、高通濾波器

- 預加重控制(Pre-emphasis)技術

預加重作用在信號的傳送端,提早增強信號的高頻成分,再透過訊號通道材料的衰減, 最後接收端將會接收到完整的信號 。

所以信號的高頻分量主要出現在信號的上升沿和下降沿處,預加重技術就是增強信號上升沿和下降沿處的幅度。如圖11所示。

圖十二、預加重波形

圖十二、預加重波形

- 去加重(De-emphasis)技術

去加重技術的思維與預加重技術有點類似,一般是由RC濾波電路來組成,如圖12所示, 只是實現方法有點不同,預加重是增加信號上升沿和下降沿處的幅度,其它地方幅度不變; 而去加重是保持信號上升沿和下降沿處的幅度不變,其他地方信號減弱。在信號傳送應用中,可以通過此方法將信號的低頻成分衰減,由此應對信號通路中高頻成分的衰減,使信號的幅度降低,造成後級電路模組識別信號的困難。現實套用中,會更多的選擇預加重的方法,如圖13所示

圖十三、RC濾波電路

圖十三、RC濾波電路

圖十四、去加重波型

圖十四、去加重波型

Redriver 架構主要又可細分為下列3種類型

2-1 Limiting Redriver

該款主要特點是它有著相對高的電壓增益(EQ),增益能達到10倍以上。 比如一個100Mv的小信號輸入,透過電壓增益(EQ)後輸出能達到1000mV。並且Limiting Redriver在發送端TX模組織中也包含了幅值(Swing)和預加重控制(Pre-emphasis )技術,如圖15所示

圖十五、透過Redriver 訊號傳遞過程波形

圖十五、透過Redriver 訊號傳遞過程波形

2-2 Linear Redriver

主要和Limiting Redriver最大的差異則是, 只有增益(EQ=Equaliztion)的部分,而沒有沒有幅值(Swing)和預加重控制(Pre-emphasis)

2-3 Non-l Linear Redriver

其特點是輸入輸出增益很小,幾乎為1:1.也就是說100mV的小信號輸入,輸出還是約略為100mV.

中繼器實際設計&應用

以一般主機板的應用來說PCH or SOC 大多都會在板子的中間,而USB connector將會分部在板子的周邊,如圖十六所示

圖十六、主機板規劃

圖十六、主機板規劃

基本上USB trace 走線一般都會超過PCH or SOC 的規範, 如此PCH or SOC廠商將無法保證訊號的品質能符合USB IF的規範, 如此中繼器(Retimer/Reriver)就派上用場,當下R&D最常問的問題就是:「中繼器要擺放在訊號線上的哪個位置?」

設計前必須收集下方3個最重要訊息

3-1. 需評估PCH or SOC 到DEVICE or CONNECTOR的所需長度大約是多少

3-2 接下來要知道PCB將會採用哪款材質 ( 不同PCB材質對於USB3.2 Gen2 訊號的 L損耗均不一樣)

3-3 最後需要知道將採用的中繼器對於訊號補償的能力如何, 如圖十七所示

圖十七、中繼器USB3.2 Gen2補償Table

圖十七、中繼器USB3.2 Gen2補償Table

現在我們以USB3.2 Gen2 Redriver的應用來做相關評估說明:

如果以PCH or SOC到DEVICE or CONNECTOR trace需要19 inch.,PCB材質以FR4為例USB3.2 Gen2 訊號trace長度 1 inch 大約訊號損耗約 0.7db左右;另外PCH or SCO SPEC USB3.2 Gen2 trace 最長可支援到8.5db約12.1 inch。依照上述相關訊息PCH or SOC最長trace 可以拉到12.1 inch, 以圖16所示中繼器最大可補償14.1 db 約 9.8db, 所以可以初估出中繼器最佳擺放位置。

註: trace 的長度都不建議拉到極限,以避免中繼器補償不足的情況

圖十八、中繼器最佳擺放位置

圖十八、中繼器最佳擺放位置

研發設計者的迷思

研發人員會採用中繼器(Retimer or Redriver)必定是遇到了因應用關係訊號傳遞長度超出關主晶片規格或多串接應用的問題,但往往會不經意遺忘PCB材質或外接CABLE材質製程所造成的損耗

一旦忽略掉上述非常重要的點,對於Retimer or Redriver的擺放位置與調整將會帶來相當大的問題, 另外資料線損耗的標準算法並非是用佈線長度(Inch) or 多少公分…等,而是要以db值來評估,如此才能選擇到合適的種類與調整出合適的參數, 如表一所示。

表一、 PCIE 訊號在FR4 損耗參考值

表一、 PCIE 訊號在FR4 損耗參考值

由上述介紹, 雖然Retimer相對於Redriver在高速訊號的傳遞有相當的優勢, 不過對於成本價架構來說也比REDRIVER高上不少, 另外RETIER可調動的參數值相對於Redriver也多上許多. 所以對於調整量測也讓相關研發人員吃盡苦頭。Redriver在雖然高速訊號的傳遞也有相當助益, 但是因技術架構問題連同訊號夾帶的雜訊也一併增強,在USB4/PCIE5以上高速訊號的傳遞將受到限制

參考文獻

- 創惟科技股份有限公司, https://www.genesyslogic.com.tw/

- 硬件设计14, https://reurl.cc/deloyM

- 预加重、去加重和均衡, https://reurl.cc/VRQo0Y

- 高速信号的预加重(Pre-emphasis)和去加重(De-emphasis), https://reurl.cc/delo1M

- 微星科技, https://tw.msi.com/

- 解決訊號衰減/失真,重計時器實現USB-C高速傳輸, https://reurl.cc/vm4xQy

- Repeater 概述, 大大通, https://reurl.cc/ym4aA2

- 高速PCB设计中隐藏的10个信号完整性问题, https://reurl.cc/zr4kQy

- 【工程师年度总结】retimer/redriver/repeater的定义以及差异, https://reurl.cc/4XvMlD

- 中繼補償傳輸通道耗損 Retimer確保訊號完整性, Joseph Juan, https://reurl.cc/gQpoNN