Treinamento FPGA Básico-Intermediário

Treinamento FPGA Altera Etapa 01

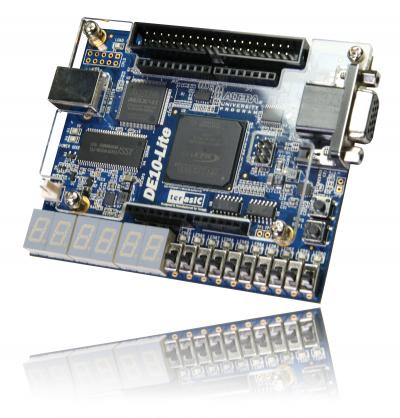

Curso teórico-prático de 20 horas utilizando o Kit FPGA DE10-Lite sem pré-requisitos

A Macnica DHW abre inscrições para o curso que é realizado online e ao vivo.

A ementa atende ao nível de conhecimento básico-intermediário em Tecnologia FPGA Altera.

O curso aborda os tópicos:

- Tecnologia FPGA Altera

- Linguagem de Descrição de Hardware Verilog

- Utilização do Software Quartus Prime Lite

- Ferramentas de Análise de Tempo (timing)

- Ferramentas de Depuração do Projeto

- Utilização do Kit FPGA DE10-Lite

- Simulação

Tornamos o Treinamento mais dinâmico, rápido e prático (Ementa Completa).

São 20 horas de carga horária distribuídas em 01 semana de curso (Agenda).

Ao fazer a inscrição o participante recebe o Kit DE10-LITE em casa.

Nossos instrutores são preparados para ministrar todos os módulos FPGA Altera, se você ou sua equipe tiver interesse em fazer outros módulos, entre em contato conosco para que possamos fazer uma Proposta voltada para sua necessidade.

Ementa simplificada

- Revisão dos conceitos de Lógica Digital utilizados no FPGA;

- Introdução à arquitetura de Lógica Programável Intel FPGA (Intel/Altera);

- Construções em Verilog necessárias para descrever a lógica no FPGA;

- Funcionalidades da ferramenta Quartus utilizada para configurar o FPGA com sua descrição em Verilog;

- Laboratórios práticos aplicando os conceitos aprendidos no Kit DE10-Lite; (incluso no Treinamento)

- Boas práticas para projetos em FPGA: Como descrever lógica da forma mais correta e robusta;

- Conceitos básicos de Timing para garantir a estabilidade do seu projeto;

- Construções mais utilizadas em projetos síncronos para lógica programável;

- Ferramentas de depuração para dispositivos Intel FPGA;

- Bônus: Conheça o Qsys! Ferramenta que permite montar um sistema com microcontrolador e periféricos em minutos.

Ementa detalhada

- Apresentação do FPGA

Revisão sobre lógica digital, contextualizando o FPGA

Introdução sobre arquitetura de processadores, comparando com o funcionamento do FPGA

Como são implementadas as portas lógicas no FPGA

Como implementar as portas lógicas em Verilog através de operadores

Arquitetura do FPGA: registradores, multiplicadores, memória, hard IPs (controlador PCIe, DDR, transceivers, etc)

- Pinos de entrada e saida, no FPGA, Verilog e Quartus

Recursos disponíveis nos pinos de entrada e saída do FPGA

Implementação em Verilog dos pinos

Mapeando os pinos do Verilog no FPGA através do Quartus: Pin Planner

Apresentação da ferramenta Quartus: principais janelas, abas, etc

Atribuições em Verilog, mapeamento de sinais internos para as entradas e saídas

Apresentação do Kit DE10-Lite: principais funcionalidades e onde obter mais recursos

Projeto 1, parte 1: Criar uma descrição de hardware em Verilog, mapear suas entradas e saídas nos pinos do FPGA, conectando botões em LEDs.

- Compilação do Quartus

Processo de compilação no Quartus

Mensagens de compilação

Formas de visualização gráfica dos resultados da compilação

Projeto 1, parte 2: Compilar o projeto criado e analisar os resultados da compilação

- Configuração do FPGA: Como funciona e como fazer

Formas de configuração suportadas pelo FPGA

Como configurar o FPGA utilizando o Quartus Programmer

Projeto 1, parte 2: Configurar o FPGA com o projeto criado e observar o comportamento

- Criação e configurações de projetos no Quartus

Passo a passo para criação de um novo projeto

Importação de configurações de projetos existentes

Configurações de projeto: arquivos e bibliotecas, opções de compilação, etc.

- Interconexões e constantes em Verilog

Interconexões: conceitos e sintaxe

Constantes numéricas: formas de representação

Projeto 2: Criar um novo projeto, importar configurações padrão para o Kit, fazer incrementos no Verilog (multiplexadores, interconexões, constantes). Compilar, visualizar o resultado, configurar o FPGA e testar

- Processos explícitos em Verilog: Always/Entendendo a simulação vs. compilação para garantir a implementação correta do hardware no FPGA

Processos combinacionais: conceito de processos, lista de sensibilidade, sintaxe em Verilog

Funcionamento da simulação (deltas/ciclos de simulação, agendamento, etc)

Como a compilação gera hardware a partir do Verilog e comparação com a simulação

Como garantir que o resultado da compilação seja equivalente ao resultado da simulação

Construções em Verilog utilizadas dentro dos processos combinacionais: if, case, loop

Projeto 3: Adicionar um processo explícito no Verilog descrevendo a mesma lógica já implementada. Compilar, visualizar o resultado, configurar o FPGA e testar.

- Registradores e clocks: implementação em Verilog e particularidades para uso no FPGA

Funcionamento de um registrador genérico e dos registradores específicos do FPGA

Boas práticas para uso de registradores em FPGA para garantir o correto funcionamento

Implementação de registradores em Verilog

Boas práticas para descrição dos registradores do FPGA em Verilog

Projeto 4: Implementar um contador síncrono com reset e enable, com a saída conectada nos LEDs. Compilar, visualizar o resultado, configurar o FPGA e testar.

- Conceitos de análise de Timing e sua aplicação no FPGA/ Boas práticas para o correto funcionamento no FPGA

Informações sobre frequência máxima nos relatórios de compilação

Importância da análise de timing

Conceitos necessários para compreender os requisitos e análise de timing

Definição de meta-estabilidade, quando ocorre e como evitar

Sentenças básicas para definição de restrições de timing em SDC

Projeto 5: Adicionar no design as estruturas recomendadas para evitar problemas de timing. Criar um arquivo SDC para o projeto. Compilar, visualizar o resultado, configurar o FPGA e testar.

- Depuração do sistema em tempo de execução usando o analisador lógico embarcado SignalTap

Instanciação do SignalTap no projeto e configuração da aquisição de dados

Uso da ferramenta para depuração

Projeto 6: Adicionar um detector de borda no sinal de enable. Instanciar o SignalTap, compilar, e iniciar a depuração. Observar possíveis problemas utilizando o SignalTap.

- Trabalhando com níveis de hierarquia no projeto

Conceito de projeto hierárquico

Sintaxe para instanciação de módulos em Verilog

Conceito de parametrização de módulos e sintaxe em Verilog

Biblioteca de IPs gratuitos e comerciais do Quartus, IP Catalog

Projeto 7: Instanciar uma memória no projeto do contador, a partir do IP Catalog. Instanciar um conversor binário para o display de 7 segmentos. Compilar, visualizar o resultado, configurar o FPGA e testar.

- Depuração do sistema em tempo de execução usando editor de memória ISMCE e a ferramenta para monitoramento e atuação do ISSP

Como funciona o monitoramento e edição de memória em tempo de execução e como habilitar

Utilização da ferramenta In-Sytem Memory Content Editor (ISMCE) para acessar a memória interna do FPGA em tempo de execução

Instanciação do componente In-System Sources and Probes (ISSP) no projeto

Utilização do ISSP para monitorar e atuar em sinais internos do FPGA em tempo de execução

Projeto 8: Habilitar ISMCE, instanciar ISSP. Compilar, configurar o FPGA e depurar o sistema em tempo de execução utilizando estas ferramentas.

- Trabalhando com máquinas de estados finitos (FSM)

Conceito de máquinas de estados

Modelagem e implementação de uma máquina de estados em Verilog

Diferentes arquiteturas de máquinas de estados, vantagens e desvantagens de cada uma

Projeto 9: Descrever em Verilog uma máquina de estados para implementar um debouncer.

- Conceito de simulação e testbench / Construções em Verilog para simulação

Conceito e utilidade da simulação e testbench

Construções em Verilog úteis para simulação

Implementação de um testbench em Verilog

Projeto 10: Implementação de um testbench em Verilog

- Simulação de módulos em Verilog utilizando a ferramenta ModelSim

Apresentação da ferramenta ModelSim

Procedimento para simulação utilizando o ModelSim

Funcionalidades básicas do ModelSim

Projeto 11: Criar um projeto do ModelSim para simulação da máquina de estados implementada. Realizar a simulação e analisar os resultados.

- Extra: Conheça o Qsys! Ferramenta que permite montar um sistema com microcontrolador e periféricos em minutos

Apresentação da ferramenta Qsys e suas principais funcionalidades.

- Em Breve: A Macnica DHW irá oferecer a continuidade do Treinamento, onde será abordado exclusivamente o Qsys e as ferramentas de software para desenvolvimento com o processador Nios, que pode ser embarcado dentro do FPGA utilizando a ferramenta do Qsys.