影响仪表放大器精度的三大因素

本文主要从原理和应用方面阐述了噪声、CMRR、PCB布局对仪表放大器精度的影响。帮助客户加深对仪表放大器参数的理解,提高电路中仪表放大器的采集精度。下面以ADI两款产品 — AD8421和AD8422为例,来分析仪表放大器的噪声、CMRR、PCB布局对精度的影响。

一、噪声对仪表放大器精度的影响

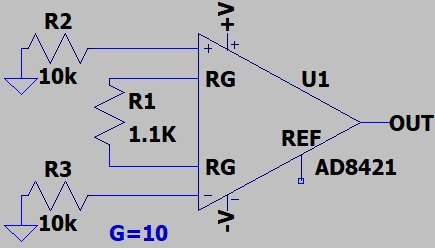

噪声的大小直接影响仪表放大器采集的精度。AD8421是一款低成本、低功耗、低噪声、低偏置电流、高速仪表放大器,特别适合各种信号调理和数据采集应用。可以在宽温度范围内,有高频共模噪声的情况下提取低电平信号。图1 以AD8421为例分析电路总噪声。基于以下假设:仪表放大器的±输入端源阻抗10KΩ,电阻另一端直接接地。

仪表放大器噪声来源包括:

- 电阻噪声(热噪声)

- 电压噪声

- 电流噪声

电阻噪声

1kΩ电阻的噪声频谱密度是 4nv/√Hz(计算公式Vn=√4KTRB), 电阻R2的噪声 VR2noise=√10*4nv/√Hz=12.6nv/√Hz;同理 VR3noise=√10*4nv/√Hz=12.6nv/√Hz;电阻R2,R3引入的总噪声 VRnoise=√12.6²+12.6²=17.9nv/√Hz;

电流噪声

AD8421电流噪声是200 fA/√Hz; 便于计算,将单位换算为 0.2pA/√Hz和10*10³Ω;电流引入的总噪声 VInoise=√(0.2*10) ²+(0.2*10) ²=2.8nv/√Hz;

电压噪声

仪表放大器有两个电压噪声,分别是输入端Eni,输出端Eno;Eno会随着仪表放大器的增益增大而减小,Eni则保持不变;AD8421的Eni最大值是3.2 nv/√Hz;Eno是60 nv/√Hz;G=10;计算增益后的Eno=6 nv/√Hz;那么电压的总噪声 VVnoise=√3.2²+6²=6.8nv/√Hz. 仪表放大器AD8421的总噪声:VTnoise=√17.9²+2.8²+6.8²=19.3nv/√Hz;

由以上计算可以发现,虽然仪表放大器有三个噪声来源,但是其主要噪声贡献来自于电阻噪声;主要噪声贡献来源于哪些具体噪声,取决于源阻抗的阻值和放大器的增益倍数。

二、CMRR对仪表放大器精度的影响

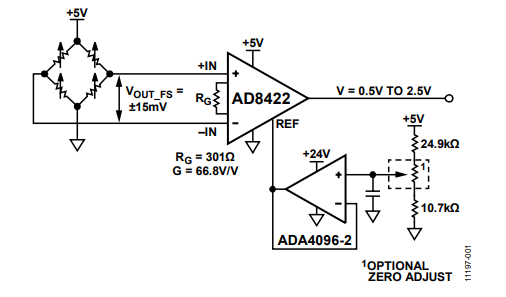

AD8422是AD620发展到第三代的产品。AD8422的低功耗,低噪声和高共模抑制比特性是测量惠斯通电桥的理想选择。图2为电桥的方案。

- 仪表放大器用来提取存在共模电压的微弱差分信号。为了保证采集精度,共模抑制比尤为重要。 共模抑制比用来描述差分增益与共模增益之比,一般用V/V或dB; CMRRV/V = ADIFF/ACM。CMRRdB = 20log(ADIFF/ACM) = 20log(ADIFF) - 20log(ACM)。

以AD8422为例,当G=1时CMRR=94dB;共模电压2.5V时,输入失调电压变化0.05mv,如果放大100倍,即 CMRR=120dB;对应输出失调电压变化 0.25mv。Vos=(Vcm/CMRR)*Gain;从公式里可以看出Vos与增益是有关系的。从上面的分析可以看出Vos的变化是非常小的,这能满足大多数客户的需求。

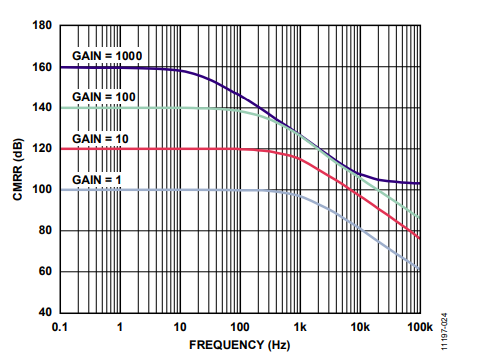

- CMRR随着仪表放大器增益变大而提高,但是也会出现一些仪表放大器在高增益时CMRR逐渐降低的情况。比如,如果一个仪表放大器CMRR=100dB;当增益提高40dB时,CMRR可能只能到125dB,这就是“CMRR压缩”,然而AD8422的CMRR可以达到160dB,这也是很少见的。

- 仪表放大器CMRR还会随着频率的增大逐渐减小,曲线中对应增益与频率之积称为增益带宽积(GBW),并且GBW是固定常数,是放大器的一个品质因数,曲线如下图3所示。

三、PCB布局对仪表放大器精度的影响

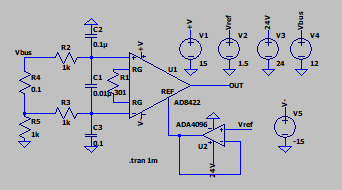

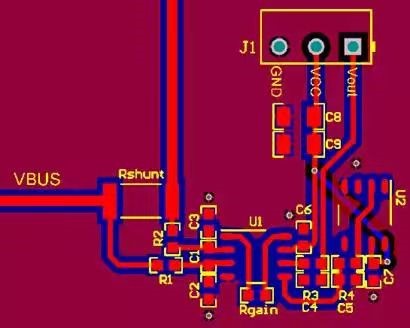

AD8422高边电流检测的应用,通过测量分流电阻R4的电压来测电流,如图4 LT spice仿真图所示:R2、C2,R3、C3提供共模滤波,R2,R3与C1提供差分滤波;U2作为缓冲INA的参考引脚,如果要降低噪声影响建议可以在U2输出端加一级低通滤波。

虽然原理图看起来简单,但是PCB布局不当,会使性能下降,影响测量精度;下面有三处PCB布局错误。如下图5所示。

PCB 布局错误1

采样电阻Rshunt到R1与R2的线路长短不等,偏置电流会给INA输入侧引入差分电压,在INA的增益倍数大的情况下,会造成较大的误差。

PCB 布局错误2

INA的增益设置电阻距离RG+和RG-的位置,线路过长会引入寄生电阻、电容,带来INA稳定性的问题,从而影响精度。

PCB 布局错误3

使用了放大器缓冲电路做为参考电压输入,同错误2一样,缓冲电路的输出到8422ref走线过长,会影响精度。

在布局中除了注意以上几点,还要注意解耦电容靠近电源引脚,更多的布局问题可以参考ADI PCB设计秘籍。

四、总结

上文分析了影响仪表放大器采集精度的因素,包括噪声,CMRR,PCB布局等。不同应用中,工程师需要关注的主要参数也不一样。电路设计时建议客户使用钻石图,LT spice仿真软件,以便验证原理功能是否满足设计预期,为后面的设计打下坚实的基础。

参考资料

更多信息:

微信平台

微信平台

FPGA 微信平台

FPGA 微信平台

領英 LinkedIn

領英 LinkedIn