基于 Intel FPGA 10 代收发器 (Native Phy) 动态重配置

本文以 Intel FPGA 10 代器件收发器 (Native Phy) 为例,阐述动态重配置的理论依据,以及介绍相关的配置流程。

动态重配置

动态重配置是指在器件运行期间,动态修改收发器通道和 PLL 以满足不断变化的要求的过程。Arria 10 收发器通道和 PLL 是完全可自定义,从而使得系统能适应其操作环境,并且能够在器件运行期间或者在上电后,通过动态触发重配置来自定义通道和 PLL。动态重配置适用于 Arria 10 / Stratix10 / Cyclone10 GX 收发器的 Native PHY / fPLL / ATX PLL / CMU PLL IP 内核。

动态重配置的常用应用需求场景

1. 改变 TX PLL 的设置来实现对多速率协议的支持;

2. 调整 TX 与 RX 模拟设置,对信号完整性进行微调;

3. 使能或禁用收发器通道模块,例如:PRBS 生成器和检查器;

4. 将 RX CDR 设置从一个数据速率修改成另一个数据速率;

5. 在多个 TX PLL 之间进行切换以支持多数据速率的支持;

6. 通过在标准型 (standard) 和增强型 (enhanced) PCS 数据通路间切换,改变 Ethernet (1G/10G) 应用中数据速率。

动态重配置支持特性

动态重配置并不能解决所有的重配置应用,下表 (表1) 对收发器通道 (发送、接收)、PLL 的重配置特性做了描述。

| 重配置 | 支持功能 | 不支持功能 |

|---|---|---|

| 通道重配置 | PMA 模拟功能 - VOD - 预加重 - 连续时间线性均衡器 (CTLE) - 判决反馈均衡 (DFE) | 从 Bonded 配置重配置为 Non- Bonded 配置,或反之; 从一种 Bonded 协议重配置为另一种 Bonded 协议 |

| TX PLL - TX 本地时钟分频器 - TX PLL 切换 | 在 Bonded 通道上更改串化因子; 在 Bonded 通道上进行 TX PLL 切换 | |

| RX CDR - RX CDR 设置 - RX CDR 参考时钟切换 | 从 PCIe (有硬核 IP) 重配置为 PCIe (无硬核 IP) 或者进行非 PCIe Bonded 协议切换 | |

| 数据通路切换 - Standard / Enhanced / PCS Direct | 进行主 CGB 重配置;在主 CGB 间切换 | |

| PLL 重配置 | PLL 设置 - 计数器 | 在 Bonded 通道上进行 TX PLL 切换 |

| PLL 参考时钟切换 |

表1 动态重配置支持特性

用户重配置接口

每个收发器通道和 PLL 包含一个 Avalon 内存映射 (Avalon-MM) 重配置接口。通过该重配置接口,可以直接访问每个通道和 PLL 的可编程空间。如果要与通道和 PLL 重配置接口进行通信,则需要一个 Avalon-MM 主端口。

由于每个通道和 PLL 都有各自的专用 Avalon-MM 接口,因此可以动态地以并发方式或按顺序修改各个通道,具体操作取决于 Avalon 主端口与 Avalon-MM 重配置接口的连接方式。Avalon-MM 的执行方式比较灵活,可以选用 FPGA 充当 Master,也可以选用 MCU,主要取决于用户的实现方案。 下图 (图1) 为用户 Avalo-MM 重配置接口简图:

图1 用户 Avalo-MM 重配置接口简图

图1 用户 Avalo-MM 重配置接口简图

发送 PLL 实例最多只能有一个重配置接口。与实例不同,Native PHY IP 内核可以指定多个通道。我们能够对每个通道使用专用的重配置接口,或者在所有通道中共享单个重配置接口来执行动态重配置。

Avalon-MM 主接口与重配置接口进行交互,即执行 Avalon 读取和写入操作来对特定收发器参数进行动态重配置初始化。所有读取和写入操作都必须符合 Avalon-MM 规范。 下图 (图2) 展示了重配置接口的顶层信号:

图2 重配置接口的顶层信号

图2 重配置接口的顶层信号

用户可访问的 Avalon-MM 重配置接口和 PreSICE Avalon-MM 接口共享一个单一的接口配置总线。

各种配置文件生成

Arria 10 收发器 Native PHY 和发送器 PLL IP 内核选择性地支持将为 IP 实例指定的参数另存为配置文件。配置文件为特定的 IP 实例存储地址和数据值。配置文件在 IP 生成期间被生成。它们位于 IP 实例的 <IP instance name>/reconfig/ 子文件夹。该配置适用于下面的格式:

- SystemVerilog packages: <name>.sv

- C Header files: <name>.h

- Memory Initialization File (MIF): <name>.mif

在收发器 Native PHY 或发送器 PLL 参数编辑器的 Dynamic Reconfiguration 选项卡上选择一个或多个配置文件格式来存储配置数据。具体步骤如下图 (图3) 所示。为特定 IP 实例生成的所有配置文件都包含相同的地址和数据值。这些配置文件的内容可用来从一种收发器 / PLL 配置重配置为另一种收发器配置。

在收发器 Native PHY IP 参数逻辑器的 Dynamic Reconfirmation 选项卡中,使能功能 Include PMA Analog settings in configuration files,如下图 (图3) 中的标记 5 所示,我们能够选择性地支持 Native PHY IP 内核将 PMA 模拟设置包含在配置文件中。

该功能在默认情况下是禁用的。使能该功能,将 Native PHY IP 参数逻辑器的 Analog PMA settings (Optional) 选项卡指定的 PMA 模拟设置添加到配置文件。Native PHY IP 参数逻辑器所选的模拟设置,它仅用于包括所选配置文件中的这些设置以及它们的相关设置。

图3 Dynamic Reconfiguration 文件选择

图3 Dynamic Reconfiguration 文件选择

多种重配置设置

我们可以选择性地在相同的 Native PHY IP 或 ATX PLL IP core Parameter Editors 中,使能多种配置或设置档来执行动态重配置。它支持 IP Parameter Editor 创建、存储和分析多种配置或设置档的参数设置。

多种重配置设置档功能时,还能实现 Native PHY 或 ATX PLL IP 内核生成配置文件用于格式所需 (SystemVerilog 封装、MIF 或 C 头文件) 的所有设置档。

该配置文件位于 IP 实例的 <IP instance name>/reconfig/ 子文件夹中,其中配置设置档索引添加到文件名。例如:Profile 0 的配置文件被存储在 <filename_CFG0.sv>。

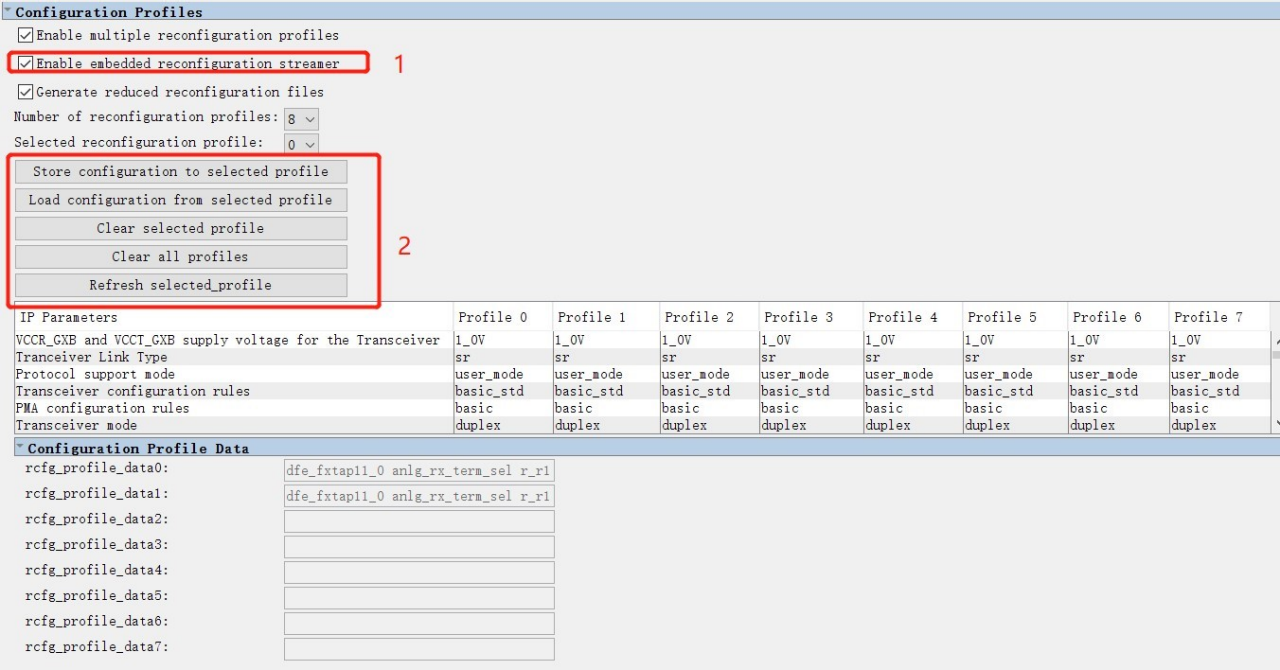

Native PHY / ATX PLL IP 内核的每个实例每次可以创建多达 8 种重配置设置档 (Profile 0 到 Profile 7)。它可以在不使用嵌入式重配置流光器功能的情况下,来使用多种重配置设置档功能。如果使用多种重配置设置档功能本身,当从一个设置档移到另一个设置档时,必须通过用户逻辑,针对设置档之间的所有不同进行重配置。下图 (图4) 为 Reconfiguration Profiles 设置步骤:

图4 Reconfiguration Profiles 设置

图4 Reconfiguration Profiles 设置

嵌入重配置方式切换

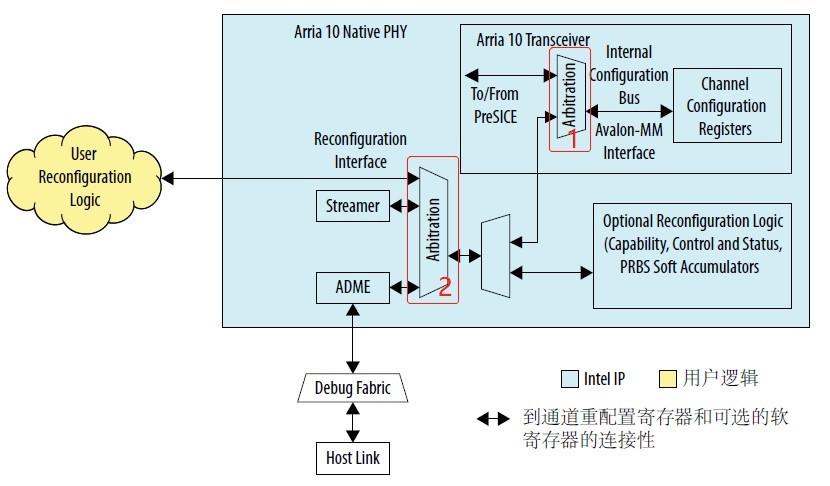

嵌入式重配置流光器是一个功能模块,它可以执行 Avalon-MM 传输来访问接收器中的通道 / ATX PLL 配置寄存器。我们能够选择性地使能 Native PHY 或 ATX PLL IP 内核中的嵌入式重配置流光器,以自动化重配置操作。

使能嵌入式流光器时,Native PHY / ATX PLL IP 内核将会嵌入 HDL 代码,用于 IP 文件中的重配置设置档存储以及重配置控制逻辑。 下图 (图5) 为嵌入式重配置简图:

图5 嵌入式重配置简图

图5 嵌入式重配置简图

在 Arria 10 器件中,有两种级别的仲裁,如上图 (图5) 的红框标记处所示:

- 通过 PreSICE 校准引擎重配置接口仲裁

- 在 Native PHY / PLL IP 中多个主端口之间的仲裁

可访问的可编程寄存器功能模块

- 嵌入式重配置流光器 (仅在 Native PHY 和 ATX PLL IP 中可用)

- ADME

- 用户重配置逻辑连接到重配置接口

当内部配置总线不属于 PreSICE 时,哪一个功能模块可以访问,取决于使能了哪个功能模块。这些功能模块对每个收发器通道 / PLL 的可编程空间的控制进行仲裁。每个功能模块通过对该通道 / PLL 执行一个读写操作,可以要求访问通道 / PLL 的可编程寄存器。

对于即将被使用的这些功能模块中的任何一个,首先必须要具有对内部配置总线的控制。而在返回总线访问 PreSICE 之前,还要必须确保这些功能模块已经完成了所有的读 / 写操作。

嵌入式重配置流光器具有最高优先权,其次是重配置接口,最后是 ADME。当两个功能模块尝试在相同的时钟周期上访问同一个收发器通道时,最高优先权的功能模块具有访问权。

唯一例外是,当一个较低优先权的功能模块正处于读 / 写操作时,而此时一个较高优先权的功能模块尝试访问相同的通道,在这种情况下,较高优先权的功能模块必须要等待较低优先权的功能模块完成读 / 写操作后,才能进行访问。

注意事项

使能设计中的 ADME 时,我们必须将 Avalon-MM 主接口连接到重配置接口,或者,连接 reconfig_clock、reconfig_reset 信号,并接地重配置接口的 reconfig_write、reconfig_read、 reconfig_address 和 reconfig_writedata 信号。如果没有正确地连接重配置接口信号,那么 ADME 将不会有时钟或复位,而 ADME 将无法实现预期的功能效果。

总结

Intel 10 代 FPGA 器件提供了灵活多变的动态重配置方式,便于工程师在实际运用中各种业务模式的切换与配置。欲了解更多技术细节和 Intel 相关方案,您可以点击下方「联系我们」,提交您的需求,我们骏龙科技公司愿意为您提供更详细的技术解答。

更多信息:

微信平台

微信平台

FPGA 微信平台

FPGA 微信平台

領英 LinkedIn

領英 LinkedIn